## GANPAT UNIVERSITY

### B. Tech. Sem. III (EC)

# Regular Examination Nov/Dec 2012 2EC304: Digital Electronics

Time: 3 Hours]

[Total Marks: 70

| T  |    |     |     |   |    |

|----|----|-----|-----|---|----|

| In | St | 111 | Cti | 0 | ns |

- 1. Attempt all questions.

- 2. Answers to the two sections must be written in separate answer books.

- 3. Figures to the right indicate full marks.

- 4. Assume suitable data, if necessary.

### **SECTION-I**

1 (A) Write a short note on different digital IC logic families.

(B) Write down the advantages of TTL and CMOS logic families in tabular form.

OR

- 1 (A) Draw and explain the circuit diagram of DTL basic NAND gate.

- (B) Explain with the help of table various versions and characteristics of TTL logic family.

- (C) Write a short note on switching time with reference to logic gate.

- (A) Draw and explain the JK flip flop using NAND implementation.

(B) Write a short note on triggering of flip flops.

- (C) Draw the excitation tables of all flip flops.

OR

- 2 (A) Explain the difference between synchronous counter and ripple counter.

Design a three bit ring synchronous counter using T flip flop.

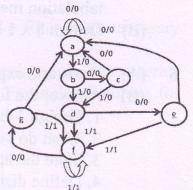

- (B) Reduce the following state diagram, mention all steps clearly and draw the reduced state diagram.

- 3 (1) Convert 7654321 to octal.

- (2) Convert 5.2545 to binary.

- Obtain 10's complement of 21210.

- (4) Obtain 2's complement of 100110.(5) Subtract M=1010101 from N=1001000.

- (6) Convert 12345 into BCD.

1

- (7) Convert 1010101 to Gray code.

- (8) Convert (11001100)g to Binary code.

- (9) Which gate is used in parity generator and checker?

- (10) Write our college name in an eight bit code made up of the seven ASCII bits and an even parity bit in the most significant position. Include blanks between names.

#### **SECTION-II**

(A) Reduce the following expressions using identities. (A+C+D)(A+C+D')(A+C'+D)(A+B')Implement the following. (B) 1. Basic gates using NAND gate 2.Basic gates using NOR gate 2 Find the compliment of following expression (C) (BC'+A'D)(AB'+CD') 2 Significance of Demorgan's theorem (D) Express the following function in sum of minterms and product of (A) maxterms. F(w,x,y,z) = y'z+wxy'+wxz'+w'x'zSimplify using K-map F (A,B,C,D)= $\sum m(0,2,4,5,6,8,10,15)$ . Draw gate level (B) implementation also Implement the Reduced function using NAND gate only. Design Binary Coded Decimal to Excess-3 code conversion using K-Map. 6 5 (A) Draw and explain a 3 to 8 line decoder. 5 (B) Simplify the Boolean function  $F(A,B,C,D) = \sum m(0,1,2,8,10,11,14,15)$  using (A) 5 tabulation method. Design 8 x 1 Multiplexer using two 4 x 1 Multiplexer 3 (B) Draw and explain 4 bit binary parallel sub tractor. 6 (A) Answer the following. (B) 2 1. Design 1-bit magnitude comparator 2 2. What do you mean by fanin and fanout? 3. State the advantages of complex MSI devices over SSI gates 4. Define distributive law. 5. Find the value of X = A B C (A+D) if A=B=C=D=16. Define Truth table.