Seat no.

# GANPAT UNIVERSITY

**B.** Tech. Semester IV Electronics & Communication Engineering **Examination May-June 2012**

# **2EC405** Digital Design using HDL

[Max. Marks: 35

3

3

# Max. Time: 2 Hrs.]

### Instructions:

- 1. Attempt all questions.

- 2. Answers to the two sections must be written in separate answer books.

- 3. Figures to the right indicate full marks.

- 4. Assume suitable data, if necessary.

## **SECTION-I**

- 1 (A) Draw and explain typical design flow for designing VLSI IC circuit.

- Which are two possible styles of stimulus application? Explain each one with 3 **(B)** the help of suitable example.

- (C) Explain 'define, 'include and 'timescale compiler directive with help of 3 example. 3

d. \$readmemb

e. \$fopen

f. \$random

- Explain the following system tasks. (A) 2

- a. \$stop

- b. \$fmonitor c. \$strobe

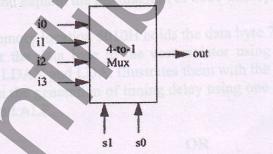

- Write a Verilog code for 4-to-1 multiplexer using gate primitive. **(B)**

What are the basic components of a module? Which components are 3 **(C)** mandatory?

- (A) Write a Verilog code for following digital circuits using continuous 3 2 assignments.

- a. 4 bit Binary to gray code converter

- b. 4 bit Odd parity checker

- (B) What would be the output/effect of the following statements?

- a. latch = 4'd12;

- \$display("The current value of latch = %b\n", latch);

- b. in reg = 3'd2;

- \$monitor(\$time, " In register value = %b\n", in reg[2:0]); c. 'define MEM SIZE 1024

- \$display("The maximum memory size is %h", 'MEM\_SIZE);

- (C) Explain various types of gate delays with suitable example?

3

3

## SECTION-II

| 3 | (A)<br>(B)        | Write a Verilog code for 4-bit ripple carry full adder by using 1-bit full adder.<br>Compare and contrast.<br>a. initial block and always block.                                                      | 33          |

|---|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|   | (C)               | b. continuous assignments and procedural assignments<br>Evaluate output Y if A=4'b1100, B=4'b1011, C=4'b101x, D=4'b1001<br>1. $Y=D+C$ 3. $Y=D >>> 1$                                                  | 2           |

|   |                   | 2. $Y = ^B$ 4. $Y = \{2\{A\}, 3\{B\}, C[0], A[1]\}$                                                                                                                                                   |             |

| 4 | (A)<br>(B)<br>(C) | Explain event based timing control in brief with the help of suitable example.<br>Write a Verilog code for 8:3 encoder using casex statement.<br>What are the differences between Task and Functions? | 3<br>3<br>3 |

|   |                   | OR COR                                                                                                                                                                                                |             |

| 4 | (A)               | Write a Verilog code for 5 bit up-down counter and check its functionality with stimulus module.                                                                                                      | 3           |

|   | (B)               | Explain different types of delay models.<br>Explain following terms with examples.                                                                                                                    | 3           |

|   | (C)               | <ul> <li>a. assign and de-assign</li> <li>b. Conditional compilation and conditional execution</li> </ul>                                                                                             | 5           |

End of Paper

(C) Explain various types of gate delays with suitable example? page 2 0 2

DOCT