## GANPAT UNIVERSITY

### B. Tech. Semester VI (EC) Regular Examination, May/June-2012

## EC604 Digital Design Using HDL its dots line and shoo golver a sm [Total Marks: 35

| Max. Time: | 2 | Hrs. |  |

|------------|---|------|--|

|------------|---|------|--|

# Instructions: Meture of the Loutena animit bezed walsh lo sager out swit (8)

- Attempt all questions.

Answers to the two sections must be written in separate answer books. 1. Attempt all questions.

- 3. Figures to the right indicate full marks.

- 4. Assume suitable data if necessary

# SECTION-I

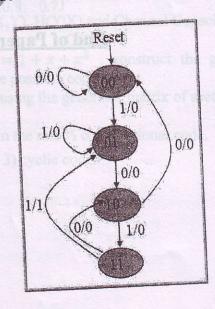

1 (A) Explain following loops with suitable example: 1. While 2. For 3. Forever 4. Repeat 5 Write a verilog program for 8:1 MUX using (B) 1. If....else statement 2. Case statement 5 Give the difference between task & function Write a verilog code for 4-bit unsigned up counter with asynchronous 4 (A) (B) clear OR 3 Explain typical design flow to design VLSI chip in detail 6 (A) Write a verilog code for following FSM (B)

### SECTION-II

(A) Write a verilog code for 4-bit latch with an inverted gate and an asynchronous preset

(B) Give the types of delay based timing control with suitable example

(A) Design verilog code for a circuit that calculates the Hamming distance of two 8-bit inputs.

(B) Explain the different system tasks and compiler directives with suitable example

OR

(A) Write a verilog code to use as a serial to parallel converter

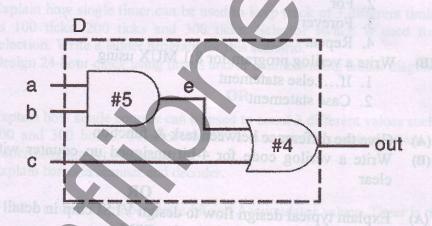

(B) Write a verilog code, testbench and draw the waveform for delay

simulation for given below diagram

#### **End of Paper**