| Student Exam No |  |

|-----------------|--|

|-----------------|--|

Total Marks:-60

# GANPAT UNIVERSITY B.TECH SEM-IV (ELECTRICAL) REGULAR EXAMINATION APRIL-JUNE 2016 2EE403: DIGITAL ELECTRONICS & MICROPROCESSOR

Time: 3 Hours

Instructions: - 1. Attempt all questions. 2. Make suitable assumptions wherever necessary. 3. Figures to the right indicate full marks. 1061 Perform the following arithmetical operations: Oue.-1 (A) (i)  $(679.6)_{BCD} + (536.8)_{BCD}$ , (ii)  $(687)_{XS-3} - (348)_{XS-3}$  (use 9's compliment method) 1041  $(ii) (105.15)_{10} = (?)_2$ (B) (i)  $(1101.11)_2 \times (101.1)_2 =$ OR (i) 2928.54 - 416.7 = (?) (using 10's compliment method) [06] Que.-1 (ii)Convert (378.93)10 to octal 1041 (B) Define the following terms: (i) XS-3 code (ii) ASCII code (iii) double dabble method.(iv)BCD code (A) Draw the circuit diagram of an edge triggered JK flip flops with 'active low preset' [05] Que.-2 and 'active low clear' using NAND gates and explain its operation with the help of truth table. Write a short note on two bit ripple up & down counter using negative edge -[05] (B) triggered flip flops. OR Que.-2 Explain the positive edge triggered transparent & toggle flip flops along with its [05] truth tables. With neat sketch, design 4-bit Parallel in, Serial out type shift register. [05] Que.-3 Attempt any Two: [10] Draw the circuit diagram of a master-salve D Flip flop and explain its operation with the help of a truth table. How is it different from edge triggering? (B) (i) What is UART? (ii) Explain the working of 4-bit buffer register.

(C) Explain half adder and full adder in detail.

## SECTION-II

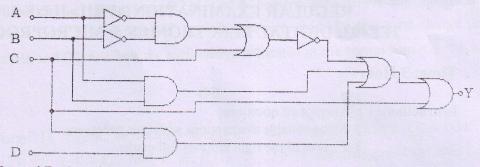

Que.-4 (A) Write the Boolean expression for the logic diagram given below and simplify it as much [04] as possible and draw the logic diagram that implements the specified reduced expression.

- (B) Expand F = (x+yz)' to min term and max term. [02] [04]

- (C) State and prove De Morgan's theorem.

### OR

Que.-4 (A) Prove that:

- [05]

- a. A'(A+B)+[(B+AA)(A+B')]=A+Bb. AB'+A(B+C)'+B(B+C)'=AB'

- (B) Reduce the expression F= \text{Em (0, 3, 4, 6, 7, 9, 12, 14, 15)} using mapping and implement [03] the reduced expression in logic diagram.

- (C) Show that AOB = AB + A'B' = (AB' + A'B)'

[02]

- (A) What are the various registers of 8085? Discuss their function. Also discuss status flags Que.-5

- Classify memory and explain demultiplexing of AD7 to AD0 in detail. (B)

[05]

[05]

Que.-5 (A) Explain function of following instruction with suitable example.

[06]

- 1. LHLD addr

- 2. XCHG

- 3. ACI data

- 4. MOV r, M

- 5. ANA M

- 6. JNC addr

- Discuss various types of addressing modes of 8085 with suitable example.

[04] [10]

#### Que.-6 Attempt any two:

- (A) Write a program to find square of a number from 0 to 9 using lookup table.

- (B) Write a program to add 16, 2B, 39 and 12 H. Numbers are placed in the memory locations 2501 to 2504 H and store the result in the memory location 2450 H.

- (C) Write an ALP to arrange a series of numbers in descending order.

# END OF PAPER