# GANPAT UNIVERSITY M. TECH SEM- III ELECTRONICS AND COMMUNITION REGULAR EXAMINATION NOV-DEC 2016 3EC301 Mixed Signal VLSI Design

# MAX. TIME: 3 HRS

## MAX. MARKS: 60

| Instruc           | tions: (1) This Question paper has two sections. Attempt each section in separate answer (2) Figures on right indicate marks.                                                    | book.        |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|

|                   | (3) Be precise and to the point in answering the descriptive questions.                                                                                                          |              |  |  |  |

|                   |                                                                                                                                                                                  |              |  |  |  |

| SECTION: I        |                                                                                                                                                                                  |              |  |  |  |

| Q.1(a)            | Explain following performance specification of DAC.                                                                                                                              | (05)         |  |  |  |

|                   | 1. Reference Voltages.                                                                                                                                                           |              |  |  |  |

|                   | <ol> <li>Settling Time</li> <li>Error</li> </ol>                                                                                                                                 |              |  |  |  |

| (b)               | Explain dual-slope ADC.                                                                                                                                                          | (05)         |  |  |  |

| (~)               | OR                                                                                                                                                                               | (00)         |  |  |  |

| Q.1(a)            | Explain binary-weighted resistor DAC.                                                                                                                                            | (05)         |  |  |  |

| (b)               | Explain flash ADC.                                                                                                                                                               | (05)         |  |  |  |

|                   |                                                                                                                                                                                  | (05)         |  |  |  |

| Q.2(a)            |                                                                                                                                                                                  |              |  |  |  |

| (b)               | Design a 3-bit DAC using a R-2R architecture with R=1k $\Omega$ , R <sub>F</sub> =2k $\Omega$ and V <sub>REF</sub> =5V.Assume that the resistance of the switches is negligible. | (05)         |  |  |  |

|                   | OR                                                                                                                                                                               |              |  |  |  |

| Q.2(a)            | Explain Basic Current Mirror Circuits with necessary derivations and waveform.                                                                                                   | (05)<br>(05) |  |  |  |

| (b)               | (b) Using superposition theorem and half circuit symmetry to derives the AC gain                                                                                                 |              |  |  |  |

|                   | equation of differential amplifier.                                                                                                                                              |              |  |  |  |

| Q.3(a)            | What are the advantages of switched capacitor filter circuits compared to RC active                                                                                              | (03)         |  |  |  |

|                   | filter circuits?                                                                                                                                                                 | (0.0)        |  |  |  |

| (b)               | Compare analog filter and digital filter circuits.<br>Determine the critical frequency of the Sallen Key low pass filter in Figure 1 and set                                     | (03)<br>(04) |  |  |  |

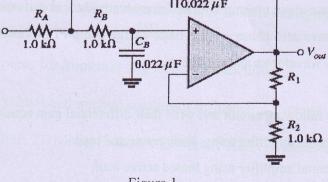

| (c)               | the value of R1 for an approximate butter-worth response.                                                                                                                        | (04)         |  |  |  |

|                   | $C_A$                                                                                                                                                                            |              |  |  |  |

|                   |                                                                                                                                                                                  |              |  |  |  |

| $R_A = R_B = R_B$ |                                                                                                                                                                                  |              |  |  |  |

|                   | Vino W +                                                                                                                                                                         |              |  |  |  |

Figure 1

### SECTION: II

- Q.4(a) Derive transfer function of simple PLL and discuss trade-off between various (05) parameters to improve its performance.

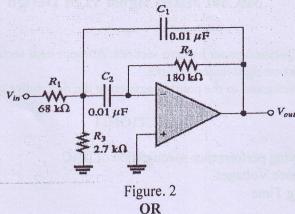

- (b) Determine the center frequency, maximum gain and bandwidth for the filter in (05) Figure 2.

Q.4(a) Show that the basic charge pump PLL behaves as low-pass filter for the jitter (05) appearing in input signal and it behaves as high-pass filter for the jitter appearing in VCO signal.

(05)

- (b) Draw the circuit diagram of following filter:

- 1. The state variable filter

- 2. The Biquad Filter

- Q.5(a) How can we realize resistor using combination of switches and capacitor? Explain (05) working of basic SC integrator circuit (with two switches), discuss the problems associated with its accuracy and draw SC integrator circuit which solves problem of basic SC integrator circuit.

- (b) Explain the effect of dead zone in charge pump circuit. How can you avoid it? (05) Explain with necessary waveforms.

#### OR

| Q.5(a)       | Explain two-stage op-amp with necessary mathematical derivation.                |                          |  |  |  |

|--------------|---------------------------------------------------------------------------------|--------------------------|--|--|--|

| (b)          | Can we have zero phase error in basic charge pump PLL? Justify your answer with |                          |  |  |  |

|              | necessary waveforms and comments.                                               |                          |  |  |  |

|              |                                                                                 |                          |  |  |  |

| Q.6(a)       | a) Draw the following circuit and write their differential gain equation:       |                          |  |  |  |

|              | 1. Differential amplifier using diode connected load.                           |                          |  |  |  |

|              | 2. Differential amplifier using biased active load.                             |                          |  |  |  |

| (b)          | b) Explain the following performance parameter for op-amp.                      |                          |  |  |  |

|              | (a) Gain                                                                        | (b) Supply and rejection |  |  |  |

|              | (c) Linearity                                                                   |                          |  |  |  |

| END OF PAPER |                                                                                 |                          |  |  |  |